Simulation software will help nanoscale architectures realise the promise of More than Moore

For the last 50 years, shrinking transistors have enabled more and more processing capacity to be put on the same size chips, following Intel co-founder Gordon Moore's predictions in the 1960s. Moore's law is reaching its physical and economic limits – our future virtually unlimited interconnectedness will depend on a paradigm shift.

Much as high-rises are a solution to urban growth, emerging 3D sequential integration could alleviate the problems faced by 2D CMOS transistor technology. Bringing this architecture down to the nanoscale could additionally enhance the already sizeable benefits.

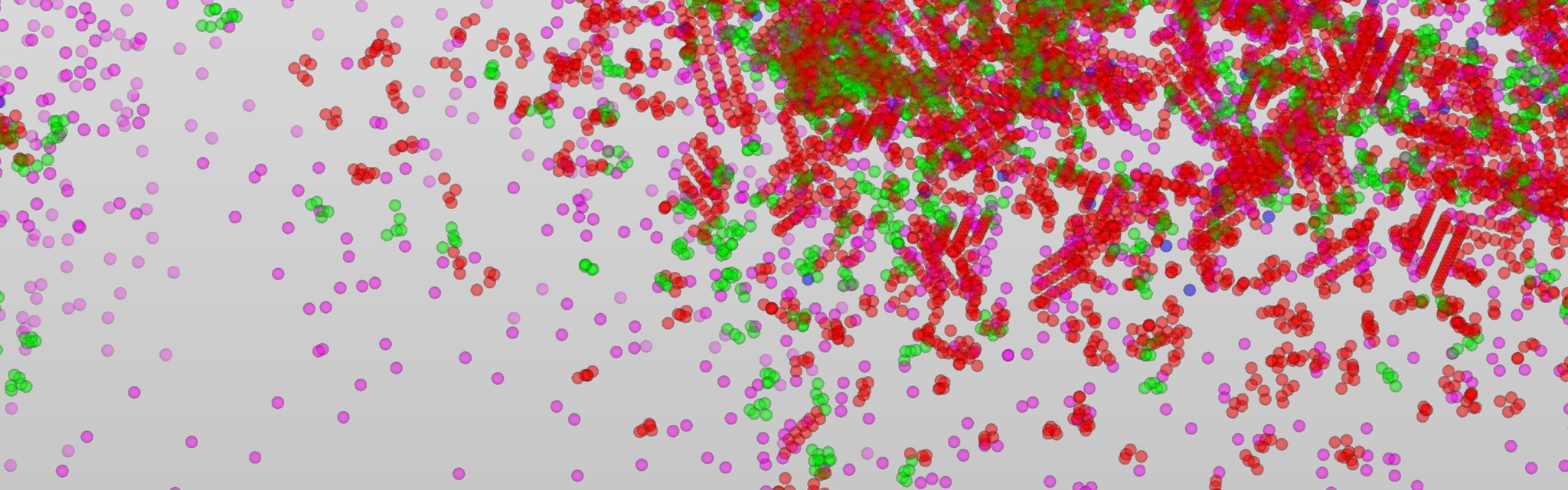

Building on extensive experimental work and data, the EU-funded MUNDFAB project has worked on developing the requisite modelling and simulation tools that will foster innovation via virtual fabrication of the next generation of nanoscale electronic devices.

Duration of project: January 1, 2020 - June 30, 2023

Last update of webpage: April 16, 2024

Modeling Unconventional Nanoscaled Device FABrication

Modeling Unconventional Nanoscaled Device FABrication